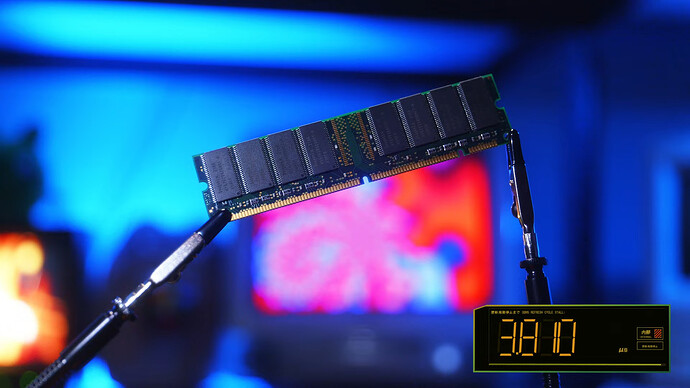

คอมพิวเตอร์สมัยใหม่พึ่งพา Dynamic RAM ซึ่งเป็นเทคโนโลยีที่ช่วยให้จัดเก็บข้อมูลได้อย่างหนาแน่น แต่มีข้อแลกเปลี่ยนคือต้องมีการรีเฟรชข้อมูลทุกๆ 3-4 ไมโครวินาที โดยใช้เวลาประมาณ 400 นาโนวินาทีเพื่อคงสภาพข้อมูลไว้ การหยุดชะงักเพียงเล็กน้อยนี้อาจฟังดูไม่สำคัญสำหรับผู้ใช้งานทั่วไป ทว่าในโลกของการซื้อขายความถี่สูง (HFT) เพียงแค่ไม่กี่นาโนวินาทีของความหน่วง (latency) ก็สามารถสร้างความแตกต่างระหว่างการชนะหรือแพ้คำสั่งซื้อได้เลยทีเดียว โดยเฉพาะอย่างยิ่งเมื่อข้อมูลที่ต้องการไม่ได้อยู่ในแคช และต้องดึงจากหน่วยความจำหลัก ซึ่งอาจทำให้ต้องรอคอยนานกว่า 400 นาโนวินาทีในจังหวะที่ไม่เหมาะสม

เพื่อหลีกเลี่ยงผลกระทบจากความหน่วงนี้ ผู้เชี่ยวชาญกำลังพิจารณาวิธีการสร้างสำเนาข้อมูลบนตัวจับเวลาการรีเฟรชอิสระสองชุด อย่างไรก็ตามแนวคิดนี้ไม่ง่ายอย่างที่คิด เนื่องจากระบบปฏิบัติการมักจะซ่อนที่อยู่ทางกายภาพของหน่วยความจำจากโปรแกรมประยุกต์ และตัวควบคุมหน่วยความจำเองก็ยังทำการสลับที่อยู่เพื่อกระจายข้อมูลไปยังชิป RAM ต่างๆ ทำให้การเข้าถึงและควบคุมการรีเฟรชข้อมูลโดยตรงเป็นเรื่องที่ท้าทายอย่างยิ่ง

สำหรับผู้ที่สนใจสถาปัตยกรรมคอมพิวเตอร์ในเชิงลึก จะมีรายละเอียดทางเทคนิคที่ซับซ้อนอีกมาก ซึ่งผู้เชี่ยวชาญได้อธิบายถึงปัญหาและแนวทางแก้ไขเหล่านี้ไว้อย่างละเอียด เพื่อค้นหาวิธีท้าทายข้อจำกัดด้านดีไซน์ของ RAM ที่มีมานานกว่าครึ่งศตวรรษ.

🏷️ หมวดหมู่: computer hacks, computer science, dynamic ram

🔗 อ่านบทความฉบับเต็ม: hackaday